Our commitment to creating and enhancing technology is all about helping the world solve challenges. It’s a big reason we created OmniXtend™, the cache-coherent memory fabric that is open source and available now for the entire industry to leverage.

We announced OmniXtend recently as part of our ongoing work utilizing RISC-V, the instruction set architecture (ISA) that will enable innovation in next-generation data-centric computing. OmniXtend is a new open approach to providing cache coherent memory over an Ethernet fabric.

This leverages the full power and promise of heterogeneous computing, the concept that today’s increasingly sophisticated systems can be improved in system performance and energy efficiency if they use more than one kind of processor or core. Adding dissimilar co-processors that can handle specific tasks using specialized processing capabilities is, as you know if you’ve followed our blogs, at the heart of our support of the fast-growing RISC-V initiative and its long-term vision for developing purpose-built compute architectures. That sort of innovation could spark growth and lead to monumental advances in data-driven applications such as artificial intelligence, machine learning, Internet of Things and architectures of the future yet to be imagined.

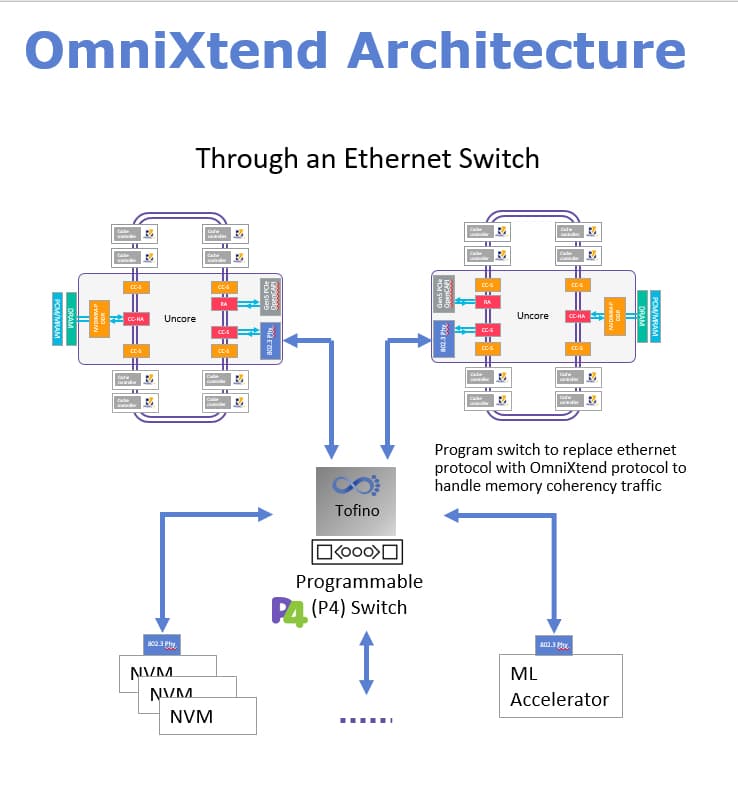

OmniXtend’s capabilities are based on an open-source architecture supported by a full spectrum of hardware, including ubiquitous Ethernet physical layer and programmable Ethernet switches, such as Barefoot’s Tofino™ P4-programmable switch.

Thanks to compatibility with the Tofino switch, architects in data centers – where main memory is central to the network – can implement innovative architectures that may support further advancements in areas including CPU micro-architecture and purpose-built compute acceleration in data-centric devices.

By using OmniXtend, system designers can take advantage of the many benefits of memory-centric architecture. Heterogeneous systems should all reside in the same memory domain and share memory in a coherent way. We can bring a new, open approach to design and enable machine-learning accelerators, custom ASICs, FPGAs, CPUs and GPUs, all able to share one memory pool through the switch. We’re very, very excited to have achieved this next-generation milestone in OmniXtend.

Watch our demo:

MORE SUPPORT FOR DEVELOPMENT: OPEN SOURCE PlatformIO TOOLS AND KEY ENHANCEMENTS FOR RISC-V SweRV Core™

Learn More

• [INNOVATIONS page] RISC-V at Western Digital

• [GITHUB repo] The SweRV Core EH1 is now open sourced for the RISC-V community to utilize and contribute to. It is available on GitHub at https://github.com/westerndigitalcorporation/swerv_eh1

• [SOCIAL MEDIA] Follow Western Digital Office of the CTO on Twitter for news, updates and discussion.